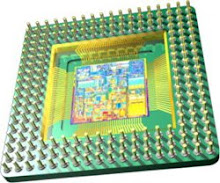

Pentium ("Classic")

- Bus width 64 bits

- System bus clock rate 60 or 66 MHz

- Address bus 32 bits

- Addressable Memory 4 GB

- Virtual Memory 64 TB

- Superscalar architecture brought 5X the performance of the 33 MHz 486DX processor

- Runs on 5 volts

- Used in desktops

- 16 KB of L1 cache

- P5 - 0.8 µm process technology

Introduced March 22, 1993

Number of transistors 3.1 million

Socket 4 273 pin PGA processor package

Package dimensions 2.16" x 2.16"

Family 5 model 1

- Variants

60 MHz with 100 MIPS (70.4 SPECint92, 55.1 SPECfp92 on Xpress 256 KB L2)

66 MHz with 112 MIPS (77.9 SPECint92, 63.6 SPECfp92 on Xpress 256 KB L2) - P54 - 0.6 µm process technology

- Socket 7 296/321 pin PGA package

- Number of transistors 3.2 million

- Variants

75 MHz Introduced October 10, 1994

90 MHz Introduced March 7, 1994

100 MHz Introduced March 7, 1994

120 MHz Introduced March 27, 1995 - P54C - 0.35 µm process technology

Number of transistors 3.3 million

90 mm² die size

Family 5 model 2

- Variants

120 MHz Introduced March, 1995

133 MHz Introduced June, 1995

150 MHz Introduced January 4, 1996

166 MHz Introduced January 4, 1996

200 MHz Introduced June 10, 1996

80386EX (Intel386 EX) (chronological entry)

- Introduced August 1994

Pentium Pro (chronological entry)

- Introduced November 1995

- P55C - 0.35 µm process technology

Introduced January 8, 1997

Intel MMX instructions

Socket 7 296/321 pin PGA (pin grid array) package

32 KB L1 cache

Number of transistors 4.5 million

System bus clock rate 66 MHz

Basic P55C is family 5 model 4, mobile are family 5 model 7 and 8 - Variants

166 MHz Introduced January 8, 1997

200 MHz Introduced January 8, 1997

233 MHz Introduced June 2, 1997

166 MHz (Mobile) Introduced January 12, 1998

200 MHz (Mobile) Introduced September 8, 1997

233 MHz (Mobile) Introduced September 8, 1997

266 MHz (Mobile) Introduced January 12, 1998

300 MHz (Mobile) Introduced January 7, 1999

32-bit processors: P6/Pentium M microarchitecture

- Introduced November 1, 1995

- Precursor to Pentium II and III

- Primarily used in server systems

- Socket 8 processor package (387 pins) (Dual SPGA)

- Number of transistors 5.5 million

- Family 6 model 1

- 0.6 µm process technology

16 KB L1 cache

256 KB integrated L2 cache

60 MHz system bus clock rate

Variants

150 MHz - 0.35 µm process technology, or 0.35 µm CPU with 0.6 µm L2 cache

Number of transistors 5.5 million

512 KB or 256 KB integrated L2 cache

60 or 66 MHz system bus clock rate

Variants

166 MHz (66 MHz bus clock rate, 512 KB 0.35µmCache)

Introduced November 1, 1995

180 MHz (60 MHz bus clock rate, 256 KB 0.6 µm cache) Introduced November 1, 1995

200 MHz (66 MHz bus clock rate, 256 KB 0.6 µm cache) Introduced November 1, 1995

200 MHz (66 MHz bus clock rate, 512 KB 0.35 µm cache) Introduced November 1, 1995

200 MHz (66 MHz bus clock rate, 1 MB 0.35 µm cache) Introduced August 18, 1997

- Introduced May 7, 1997

- Pentium Pro with MMX and improved 16-bit performance

- 242-pin Slot 1 (SEC) processor package

- Slot 1

- Number of transistors 7.5 million

- 32 KB L1 cache

- 512 KB ½ bandwidth external L2 cache

- The only Pentium II that did not have the L2 cache at ½ bandwidth of the core was the Pentium II 450 PE.

- Klamath - 0.35 µm process technology (233, 266, 300 MHz)

66 MHz system bus clock rate

Family 6 model 3

Variants

233 MHz Introduced May 7, 1997

266 MHz Introduced May 7, 1997

300 MHz Introduced May 7, 1997 - Deschutes - 0.25 µm process technology (333, 350, 400, 450 MHz)

Introduced January 26, 1998

66 MHz system bus clock rate (333 MHz variant), 100 MHz system bus clock rate for all models after

Family 6 model 5

Variants

333 MHz Introduced January 26, 1998

350 MHz Introduced April 15, 1998

400 MHz Introduced April 15, 1998

450 MHz Introduced August 24, 1998

233 MHz (Mobile) Introduced April 2, 1998

266 MHz (Mobile) Introduced April 2, 1998

333 MHz Pentium II Overdrive processor for Socket 8 Introduced August 10, 1998

300 MHz (Mobile) Introduced September 9, 1998

333 MHz (Mobile)

Celeron (Pentium II-based)

- Covington - 0.25 µm process technology

Introduced April 15, 1998

242-pin Slot 1 SEPP (Single Edge Processor Package)

Number of transistors 7.5 million

66 MHz system bus clock rate

Slot 1

32 KB L1 cache

No L2 cache

Variants

266 MHz Introduced April 15, 1998

300 MHz Introduced June 9, 1998 - Mendocino - 0.25 µm process technology

Introduced August 24, 1998

242-pin Slot 1 SEPP (Single Edge Processor Package), Socket 370 PPGA package

Number of transistors 19 million

66 MHz system bus clock rate

Slot 1, Socket 370

32 KB L1 cache

128 KB integrated cache

Family 6 model 6

Variants

300 A MHz Introduced August 24, 1998

333 MHz Introduced August 24, 1998

366 MHz Introduced January 4, 1999

400 MHz Introduced January 4, 1999

433 MHz Introduced March 22, 1999

466 MHz

500 MHz Introduced August 2, 1999

533 MHz Introduced January 4, 2000

266 MHz (Mobile)

300 MHz (Mobile)

333 MHz (Mobile) Introduced April 5, 1999

366 MHz (Mobile)

400 MHz (Mobile)

433 MHz (Mobile)

450 MHz (Mobile) Introduced February 14, 2000

466 MHz (Mobile)

500 MHz (Mobile) Introduced February 14, 2000

Pentium II Xeon (chronological entry)

- Katmai - 0.25 µm process technology

Introduced February 26, 1999

Improved PII, i.e. P6-based core, now including Streaming SIMD Extensions (SSE)

Number of transistors 9.5 million

512 KB ½ bandwidth L2 External cache

242-pin Slot 1 SECC2 (Single Edge Contact cartridge 2) processor package

System Bus clock rate 100 MHz, 133 MHz (B-models)

Slot 1

Family 6 model 7

Variants

450 MHz Introduced February 26, 1999

500 MHz Introduced February 26, 1999

550 MHz Introduced May 17, 1999

600 MHz Introduced August 2, 1999

533 MHz Introduced (133 MHz bus clock rate) September 27, 1999

600 MHz Introduced (133 MHz bus clock rate) September 27, 1999 - Coppermine - 0.18 µm process technology

Introduced October 25, 1999

Number of transistors 28.1 million

256 KB Advanced Transfer L2 Cache (Integrated)

242-pin Slot-1 SECC2 (Single Edge Contact cartridge 2) processor package, 370-pin FC-PGA (Flip-chip pin grid array) package

System Bus clock rate 100 MHz (E-models), 133 MHz (EB models)

Slot 1, Socket 370

Family 6 model 8

Variants

500 MHz (100 MHz bus clock rate)

533 MHz

550 MHz (100 MHz bus clock rate)

600 MHz

600 MHz (100 MHz bus clock rate)

650 MHz (100 MHz bus clock rate) Introduced October 25, 1999

667 MHz Introduced October 25, 1999

700 MHz (100 MHz bus clock rate) Introduced October 25, 1999

733 MHz Introduced October 25, 1999

750 MHz (100 MHz bus clock rate) Introduced December 20, 1999

800 MHz (100 MHz bus clock rate) Introduced December 20, 1999

850 MHz (100 MHz bus clock rate) Introduced March 20, 2000

866 MHz Introduced March 20, 2000

933 MHz Introduced May 24, 2000

1000 MHz Introduced March 8, 2000 (Not widely available at time of release)

1100 MHz

1133 MHz (first version recalled, later re-released)

400 MHz (Mobile) Introduced October 25, 1999

450 MHz (Mobile) Introduced October 25, 1999

500 MHz (Mobile) Introduced October 25, 1999

600 MHz (Mobile) Introduced January 18, 2000

650 MHz (Mobile) Introduced January 18, 2000

700 MHz (Mobile) Introduced April 24, 2000

750 MHz (Mobile) Introduced June 19, 2000

800 MHz (Mobile) Introduced September 25, 2000

850 MHz (Mobile) Introduced September 25, 2000

900 MHz (Mobile) Introduced March 19, 2001

1000 MHz (Mobile) Introduced March 19, 2001 - Tualatin - 0.13 µm process technology

Introduced July 2001

Number of transistors 28.1 million

32 KB L1 cache

256 KB or 512 KB Advanced Transfer L2 cache (Integrated)

370-pin FC-PGA2 (Flip-chip pin grid array) package

133 MHz system bus clock rate

Socket 370

Family 6 model 11

Variants

1133 MHz (256 KB L2)

1133 MHz (512 KB L2)

1200 MHz

1266 MHz (512 KB L2)

1333 MHz

1400 MHz (512 KB L2)

Pentium II and III Xeon

- PII Xeon

Variants

400 MHz Introduced June 29, 1998

450 MHz (512 KB L2 Cache) Introduced October 6, 1998

450 MHz (1 MB and 2 MB L2 Cache) Introduced January 5, 1999 - PIII Xeon

Introduced October 25, 1999

Number of transistors: 9.5 million at 0.25 µm or 28 million at 0.18 µm)

L2 cache is 256 KB, 1 MB, or 2 MB Advanced Transfer Cache (Integrated)

Processor Package Style is Single Edge Contact Cartridge (S.E.C.C.2) or SC330

System Bus clock rate 133 MHz (256 KB L2 cache) or 100 MHz (1 - 2 MB L2 cache)

System Bus Width 64 bit

Addressable memory 64 GB

Used in two-way servers and workstations (256 KB L2) or 4- and 8-way servers (1 - 2 MB L2)

Family 6 model 10

Variants

500 MHz (0.25 µm process) Introduced March 17, 1999

550 MHz (0.25 µm process) Introduced August 23, 1999

600 MHz (0.18 µm process, 256 KB L2 cache) Introduced October 25, 1999

667 MHz (0.18 µm process, 256 KB L2 cache) Introduced October 25, 1999

733 MHz (0.18 µm process, 256 KB L2 cache) Introduced October 25, 1999

800 MHz (0.18 µm process, 256 KB L2 cache) Introduced January 12, 2000

866 MHz (0.18 µm process, 256 KB L2 cache) Introduced April 10, 2000

933 MHz (0.18 µm process, 256 KB L2 cache)

1000 MHz (0.18 µm process, 256 KB L2 cache) Introduced August 22, 2000

700 MHz (0.18 µm process, 1 - 2 MB L2 cache) Introduced May 22, 2000

Celeron (Pentium III Coppermine-based)

- Coppermine-128, 0.18 µm process technology

Introduced March, 2000

Streaming SIMD Extensions (SSE)

Socket 370, FC-PGA processor package

Number of transistors 28.1 million

66 MHz system bus clock rate, 100 MHz system bus clock rate from January 3, 2001

32 kB L1 cache

128 kB Advanced Transfer L2 cache

Family 6 model 8

Variants

533 MHz

566 MHz

600 MHz

633 MHz Introduced June 26, 2000

667 MHz Introduced June 26, 2000

700 MHz Introduced June 26, 2000

733 MHz Introduced November 13, 2000

766 MHz Introduced November 13, 2000

800 MHz Introduced January 3, 2001

850 MHz Introduced April 9, 2001

900 MHz Introduced July 2, 2001

950 MHz Introduced August 31, 2001

1000 MHz Introduced August 31, 2001

1100 MHz Introduced August 31, 2001

550 MHz (Mobile)

600 MHz (Mobile) Introduced June 19, 2000

650 MHz (Mobile) Introduced June 19, 2000

700 MHz (Mobile) Introduced September 25, 2000

750 MHz (Mobile) Introduced March 19, 2001

800 MHz (Mobile)

850 MHz (Mobile) Introduced July 2, 2001

600 MHz (LV Mobile)

500 MHz (ULV Mobile) Introduced January 30, 2001

600 MHz (ULV Mobile)

XScale (chronological entry)

Pentium 4 (not 4EE, 4E, 4F), Itanium, P4-based Xeon, Itanium 2 (chronological entries)

Celeron (Pentium III Tualatin-based)

32 KB L1 cache

256 KB Advanced Transfer L2 cache

100 MHz system bus clock rate

Socket 370

Family 6 model 11

Variants

1.0 GHz

1.1 GHz

1.2 GHz

1.3 GHz

1.4 GHz

- Banias 0.13 µm process technology

Introduced March 2003

64 KB L1 cache

1 MB L2 cache (integrated)

Based on Pentium III core, with SSE2 SIMD instructions and deeper pipeline

Number of transistors 77 million

Micro-FCPGA, Micro-FCBGA processor package

Heart of the Intel mobile Centrino system

400 MHz Netburst-style system bus

Family 6 model 9

Variants

900 MHz (Ultra low voltage)

1.0 GHz (Ultra low voltage)

1.1 GHz (Low voltage)

1.2 GHz (Low voltage)

1.3 GHz

1.4 GHz

1.5 GHz

1.6 GHz

1.7 GHz - Dothan 0.09 µm (90 nm) process technology

Introduced May 2004

2 MB L2 cache

Revised data prefetch unit

400 MHz Netburst-style system bus

21W TDP

Variants

1.00 GHz (Pentium M 723) (Ultra low voltage, 5W TDP)

1.10 GHz (Pentium M 733) (Ultra low voltage, 5W TDP)

1.20 GHz (Pentium M 753) (Ultra low voltage, 5W TDP)

1.30 GHz (Pentium M 718) (Low voltage, 10W TDP)

1.40 GHz (Pentium M 738) (Low voltage, 10W TDP)

1.50 GHz (Pentium M 758) (Low voltage, 10W TDP)

1.60 GHz (Pentium M 778) (Low voltage, 10W TDP)

1.40 GHz (Pentium M 710)

1.50 GHz (Pentium M 715)

1.60 GHz (Pentium M 725)

1.70 GHz (Pentium M 735)

1.80 GHz (Pentium M 745)

2.00 GHz (Pentium M 755)

2.10 GHz (Pentium M 765) - Dothan 533 0.09 µm (90 nm) process technology

Introduced Q1 2005

Same as Dothan except with a 533 MHz NetBurst-style system bus and 27W TDP

Variants

1.60 GHz (Pentium M 730)

1.73 GHz (Pentium M 740)

1.86 GHz (Pentium M 750)

2.00 GHz (Pentium M 760)

2.13 GHz (Pentium M 770)

2.26 GHz (Pentium M 780) - Stealey 0.09 µm (90 nm) process technology

Introduced Q2 2007

512 KB L2, 3W TDP

Variants

600 MHz (A100)

800 MHz (A110)

- Banias-512 0.13 µm process technology

Introduced March 2003

64 KB L1 cache

512 KB L2 cache (integrated)

SSE2 SIMD instructions

No SpeedStep technology, is not part of the 'Centrino' package

Family 6 model 9

Variants

310 - 1.20 GHz

320 - 1.30 GHz

330 - 1.40 GHz

340 - 1.50 GHz - Dothan-1024 90 nm process technology

64 KB L1 cache

1 MB L2 cache (integrated)

SSE2 SIMD instructions

No SpeedStep technology, is not part of the 'Centrino' package

Variants

350 - 1.30 GHz

350J - 1.30 GHz, with Execute Disable bit

360 - 1.40 GHz

360J - 1.40 GHz, with Execute Disable bit

370 - 1.50 GHz, with Execute Disable bit

Family 6, Model 13, Stepping 380 - 1.60 GHz, with Execute Disable bit

390 - 1.70 GHz, with Execute Disable bit - Yonah-1024 65 nm process technology

64 KB L1 cache

1 MB L2 cache (integrated)

SSE3 SIMD instructions, 533 MHz front-side bus, execute-disable bit

No SpeedStep technology, is not part of the 'Centrino' package

Variants

410 - 1.46 GHz

420 - 1.60 GHz,

423 - 1.06 GHz (ultra low voltage)

430 - 1.73 GHz

440 - 1.86 GHz

443 - 1.20 GHz (ultra low voltage)

450 - 2.00 GHz

- Yonah 0.065 µm (65 nm) process technology

Introduced January 2006

667 MHz frontside bus

2 MB (Shared on Duo) L2 cache

SSE3 SIMD instructions

31W TDP (T**** versions)

Variants:

Intel Core Duo T2700 2.33 GHz

Intel Core Duo T2600 2.16 GHz

Intel Core Duo T2500 2 GHz

Intel Core Duo T2450 2 GHz

Intel Core Duo T2400 1.83 GHz

Intel Core Duo T2300 1.66 GHz

Intel Core Duo T2050 1.6 GHz

Intel Core Duo T2300e 1.66 GHz

Intel Core Duo T2080 1.73 GHz

Intel Core Duo L2500 1.83 GHz (Low voltage, 15W TDP)

Intel Core Duo L2400 1.66 GHz (Low voltage, 15W TDP)

Intel Core Duo L2300 1.5 GHz (Low voltage, 15W TDP)

Intel Core Duo U2500 1.2 GHz (Ultra low voltage, 9W TDP)

Intel Core Solo T1350 1.86 GHz (533 FSB)

Intel Core Solo T1300 1.66 GHz

Intel Core Solo T1200 1.5 GHz [3]

Dual-Core Xeon LV

- Sossaman 0.065 µm (

Introduced March 2006

Based on Yonah core, with SSE3 SIMD instructions

667 MHz frontside bus

2 MB Shared L2 cache

Variants

2.0 GHz

- 0.065 µm (65 nm) process technology

533 MHz frontside bus

1 MB Shared L2 cache

SSE3 SIMD instructions

Variants:

Pentium dual-core T2130 1.86 GHz

Pentium dual-core T2080 1.73 GHz

Pentium dual-core T2060 1.60 GHz

No comments:

Post a Comment