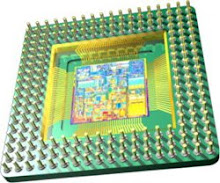

32-bit processors: NetBurst micro architecture

- 0.18 µm process technology (1.40 and 1.50 GHz)

Introduced November 20, 2000

L2 cache was 256 KB Advanced Transfer Cache (Integrated)

Processor Package Style was PGA423, PGA478

System Bus clock rate 400 MHz

SSE2 SIMD Extensions

Number of Transistors 42 million

Used in desktops and entry-level workstations - 0.18 µm process technology (1.7 GHz)

Introduced April 23, 2001 - 0.18 µm process technology (1.6 and 1.8 GHz)

Introduced July 2, 2001

Core Voltage is 1.15 volts in Maximum Performance Mode; 1.05 volts in battery

Optimized Mode

Power <1>

- 0.18 µm process technology Willamette (1.9 and 2.0 GH0z)

Introduced August 27, 2001

Family 15 model 1 - Pentium 4 (2 GHz, 2.20 GHz)

Introduced January 7, 2002 - Pentium 4 (2.4 GHz)

Introduced April 2, 2002 - 0.13 µm process technology Northwood A (1.7, 1.8, 1.9, 2, 2.2, 2.4, 2.5, 2.6, 2.8(OEM),3.0(OEM) GHz)

Improved branch prediction and other microcodes tweaks

512 KB integrated L2 cache

Number of transistors 55 million

400 MHz system bus. - Family 15 model 2

- 0.13 µm process technology Northwood B (2.26, 2.4, 2.53, 2.66, 2.8, 3.06 GHz)

533 MHz system bus. (3.06 includes Intel's hyper threading technology).

0.13 µm process technology Northwood C (2.4, 2.6, 2.8, 3.0, 3.2, 3.4 GHz)

800 MHz system bus (all versions include Hyper Threading)

6500 to 10000 MIPS

Itanium (chronological entry)

- Introduced 2001

- Official designation now Xeon, i.e. not "Pentium 4 Xeon"

- Xeon 1.4, 1.5, 1.7 GHz

Introduced May 21, 2001

L2 cache was 256 KB Advanced Transfer Cache (Integrated)

Processor Package Style was Organic Land Grid Array 603 (OLGA 603)

System Bus clock rate 400 MHz

SSE2 SIMD Extensions

Used in high-performance and mid-range dual processor enabled workstations - Xeon 2.0 GHz and up to 3.6 GHz

Introduced September 25, 2001

Itanium 2 (chronological entry)

- Introduced July 2002

Mobile Pentium 4-M

- 0.13 µm process technology

- 55 million transistors

- cache L2 512 KB

- BUS a 400 MHz

- Supports up to 1 GB of DDR 266 MHz Memory

- Supports ACPI 2.0 and APM 1.2 System Power Management

- 1.3 V - 1.2 V (SpeedStep)

- Power: 1.2 GHz 20.8 W, 1.6 GHz 30 W, 2.6 GHz 35 W

- Sleep Power 5 W (1.2 V)

- Deeper Sleep Power = 2.9 W (1.0 V)

1.40 GHz - 23 April 2002

1.50 GHz - 23 April 2002

1.60 GHz - 4 March 2002

1.70 GHz - 4 March 2002

1.80 GHz - 23 April 2002

1.90 GHz - 24 June 2002

2.00 GHz - 24 June 2002

2.20 GHz - 16 September 2002

2.40 GHz - 14 January 2003

2.40 GHz - 14 January 2003

2.50 GHz - 16 April 2003

2.60 GHz - 11 June 2003

- Introduced September 2003

- EE = "Extreme Edition"

- Built from the Xeon's "Gallatin" core, but with 2 MB cache

Pentium 4E

- Introduced February 2004

- built on 0.09 µm (90 nm) process technology Prescott (2.4A, 2.8, 2.8A, 3.0, 3.2, 3.4, 3.6, 3.8) 1 MB L2 cache

- 533 MHz system bus (2.4A and 2.8A only)

- Number of Transistors 125 million on 1 MB Models

- Number of Transistors 169 million on 2 MB Models

- 800 MHz system bus (all other models)

- Hyper-Threading support is only available on CPUs using the 800 MHz system bus.

- The processor's integer instruction pipeline has been increased from 20 stages to 31 stages, which theoretically allows for even greater bandwidth.

- 7500 to 11000 MIPS

- LGA-775 versions are in the 5xx series (32-bit) and 5x1 series (with Intel 64)

- The 6xx series has 2 MB L2 cache and Intel 64

Pentium 4F

- Introduced Spring 2004

- same core as 4E, "Prescott"

- 3.2–3.6 GHz

- starting with the D0 stepping of this processor, Intel 64 64-bit extensions has also been incorporated

64-bit processors: IA-64

- New instruction set, not at all related to x86.

- Before the feature was eliminated (Montecito, July 2006) IA-64 processors supported 32-bit x86 in hardware, but slowly

- Code name Merced

- Family 0x07

- Released May 29, 2001

- 733 MHz and 800 MHz

- 2MB cache

- All recalled and replaced by Itanium-II

- Family 0x1F

- Released July 2002

- 900 MHz - 1.6 GHz

- McKinley 900MHz 1.5MB cache, Model 0x0

- McKinley 1GHz, 3MB cache, Model 0x0

- Deerfield 1GHz, 1.5MB cache, Model 0x1

- Madison 1.3GHz, 3MB cache, Model 0x1

- Madison 1.4GHz, 4MB cache, Model 0x1

- Madison 1.5GHz, 6MB cache, Model 0x1

- Madison 1.67GHz, 9MB cache, Model 0x1

- Hondo 1.4GHz, 4MB cache, dual core MCM, Model 0x1

Pentium M (chronological entry)

- Introduced March 2003

Pentium 4EE, 4E (chronological entries)

- Introduced September 2003, February 2004, respectively

64-bit processors: Intel 64 - NetBurst

- Intel Extended Memory 64 Technology

- Mostly compatible with AMD's AMD64 architecture

- Introduced Spring 2004, with the Pentium 4F (D0 and later P4 steppings)

Pentium 4F

- Prescott-2M built on 0.09 µm (90 nm) process technology

- 2.8-3.8 GHz (model numbers 6x0)

- Introduced February 20, 2005

- Same features as Prescott with the addition of:-

2 MB cache

Intel 64bit

Enhanced Intel SpeedStep Technology (EIST) - Cedar Mill built on 0.065 µm (65 nm) process technology

- 3.0-3.6 (model numbers 6x1)

- Introduced January 16, 2006

- die shrink of Prescott-2M

- Same features as Prescott-2M

Main article: List of Intel Pentium D microprocessors

- Dual-core microprocessor

- No Hyper-Threading

- 800(4x200) MHz front side bus

- Smithfield - 90 nm process technology (2.66–3.2 GHz)

Introduced May 26, 2005

2.66–3.2 GHz (model numbers 805-840)

Number of Transistors 230 million

1 MB x 2 (non-shared, 2 MB total) L2 cache

Cache coherency between cores requires communication over the FSB

Performance increase of 60% over similarly clocked Prescott

2.66 GHz (533 MHz FSB) Pentium D 805 introduced December 2005

Contains 2x Prescott dies in one package

- Presler - 65 nm process technology (2.8–3.6 GHz)

Introduced January 16, 2006

2.8–3.6 GHz (model numbers 915-960)

Number of Transistors 376 million

2 MB x 2 (non-shared, 4 MB total) L2 cache

Contains 2x Cedar Mill dies in one package

- Dual-core microprocessor

- Enabled Hyper-Threading

- 800(4x200) MHz front side bus

- Smithfield - 90 nm process technology (3.2 GHz)

Variants

Pentium 840 EE - 3.20 GHz (2 x 1 MB L2) - Presler - 65 nm process technology (3.46, 3.73)

2 MB x 2 (non-shared, 4 MB total) L2 cache

Variants

Pentium 955 EE - 3.46 GHz

Pentium 965 EE - 3.73 GHz

- Nocona

Introduced 2004 - Irwindale

Introduced 2004 - Cranford

Introduced April 2005

MP version of Nocona - Potomac

Introduced April 2005

Cranford with 8 MB of L3 cache - Paxville DP (2.8 GHz)

Introduced October 10, 2005

Dual-core version of Irwindale, with 4 MB of L2 Cache (2 MB per core)

2.8 GHz

800 MT/s front side bus - Paxville MP - 90 nm process (2.67 - 3.0 GHz)

Introduced November 1, 2005

Dual-Core Xeon 7000 series

MP-capable version of Paxville DP

2 MB of L2 Cache (1 MB per core) or 4 MB of L2 (2 MB per core)

667 MT/s FSB or 800 MT/s FSB - Dempsey - 65 nm process (2.67 - 3.73 GHz)

Introduced May 23, 2006

Dual-Core Xeon 5000 series

MP version of Presler

667 MT/s or 1066 MT/s FSB

4 MB of L2 Cache (2 MB per core)

Socket J, also known as LGA 771. - Tulsa - 65 nm process (2.5 - 3.4 GHz)

Introduced August 29, 2006

Dual-Core Xeon 7100-series

Improved version of Paxville MP

667 MT/s or 800 MT/s FSB

64-bit processors: Intel 64 - Core microarchitecture

- Woodcrest - 65 nm process technology

Server and Workstation CPU (SMP support for dual CPU system)

Introduced June 26, 2006

Dual-Core

Intel VT, multiple OS support

EIST (Enhanced Intel SpeedStep Technology) in 5140, 5148LV, 5150, 5160

Execute Disable Bit

TXT, enhanced security hardware extensions

SSSE3 SIMD instructions

iAMT2 (Intel Active Management Technology), remotely manage computers - Variants

Xeon 5160 - 3.00 GHz (4 MB L2, 1333 MHz FSB, 80 W)

Xeon 5150 - 2.66 GHz (4 MB L2, 1333 MHz FSB, 65 W)

Xeon 5140 - 2.33 GHz (4 MB L2, 1333 MHz FSB, 65 W)

Xeon 5130 - 2.00 GHz (4 MB L2, 1333 MHz FSB, 65 W)

Xeon 5120 - 1.86 GHz (4 MB L2, 1066 MHz FSB, 65 W)

Xeon 5110 - 1.60 GHz (4 MB L2, 1066 MHz FSB, 65 W)

Xeon 5148LV - 2.33 GHz (4 MB L2, 1333 MHz FSB, 40 W) -- Low Voltage Edition - Clovertown - 65 nm process technology

Server and Workstation CPU (SMP support for dual CPU system)

Introduced Dec 13th 2006

Quad Core

Intel VT, multiple OS support

EIST (Enhanced Intel SpeedStep Technology) in E5365, L5335

Execute Disable Bit

TXT, enhanced security hardware extensions

SSSE3 SIMD instructions

iAMT2 (Intel Active Management Technology), remotely manage computers - Variants

Xeon X5355 - 2.66 GHz (2x4 MB L2, 1333 MHz FSB, 105 W)

Xeon E5345 - 2.33 GHz (2x4 MB L2, 1333 MHz FSB, 80 W)

Xeon E5335 - 2.00 GHz (2x4 MB L2, 1333 MHz FSB, 80 W)

Xeon E5320 - 1.86 GHz (2x4 MB L2, 1066 MHz FSB, 65 W)

Xeon E5310 - 1.60 GHz (2x4 MB L2, 1066 MHz FSB, 65 W)

Xeon L5320 - 1.86 GHz (2x4 MB L2, 1066 MHz FSB, 50 W)-- Low Voltage Edition

- Conroe - 65 nm process technology

Desktop CPU (SMP support restricted to 2 CPUs)

Two cores on one die

Introduced July 27, 2006

SSSE3 SIMD instructions

Number of Transistors 291 Million

Intel VT, multiple OS support

TXT, enhanced security hardware extensions

Execute Disable Bit

EIST (Enhanced Intel SpeedStep Technology)

iAMT2 (Intel Active Management Technology), remotely manage computers

LGA775

Variants

Core 2 Duo E6850 - 3.00 GHz (4 MB L2, 1333 MHz FSB)

Core 2 Duo X6800 - 2.93 GHz (4 MB L2, 1066 MHz FSB)

Core 2 Duo E6750 - 2.67 GHz (4 MB L2, 1333 MHz FSB)

Core 2 Duo E6700 - 2.67 GHz (4 MB L2, 1066 MHz FSB)

Core 2 Duo E6600 - 2.40 GHz (4 MB L2, 1066 MHz FSB)

Core 2 Duo E6550 - 2.33 GHz (4 MB L2, 1333 MHz FSB)

Core 2 Duo E6420 - 2.13 GHz (4 MB L2, 1066 MHz FSB)

Core 2 Duo E6400 - 2.13 GHz (2 MB L2, 1066 MHz FSB)

Core 2 Duo E6320 - 1.86 GHz (4 MB L2, 1066 MHz FSB)

Core 2 Duo E6300 - 1.86 GHz (2 MB L2, 1066 MHz FSB) - Conroe XE - 65 nm process technology

Desktop Extreme Edition CPU (SMP support restricted to 2 CPUs)

Introduced July 27, 2006

same features as Conroe

LGA775

Variants

Core 2 Extreme X6800 - 2.93 GHz (4 MB L2, 1066 MHz FSB) - Allendale - 65 nm process technology

Desktop CPU (SMP support restricted to 2 CPUs)

Two CPUs on one die

Introduced January 21, 2007

SSSE3 SIMD instructions

Number of Transistors 167 Million

TXT, enhanced security hardware extensions

Execute Disable Bit

EIST (Enhanced Intel SpeedStep Technology)

iAMT2 (Intel Active Management Technology), remotely manage computers

LGA775

Variants

Core 2 Duo E4600 - 2.40 GHz (2 MB L2, 800 MHz FSB)

Core 2 Duo E4500 - 2.20 GHz (2 MB L2, 800 MHz FSB)

Core 2 Duo E4400 - 2.00 GHz (2 MB L2, 800 MHz FSB)

Core 2 Duo E4300 - 1.80 GHz (2 MB L2, 800 MHz FSB) - Merom - 65 nm process technology

Mobile CPU (SMP support restricted to 2 CPUs)

Introduced July 27, 2006

Family 6, Model 15, Stepping 10

same features as Conroe

Socket M / Socket P

Variants

Core 2 Duo T7800 - 2.60 GHz (4 MB L2, 800 MHz FSB) (Santa Rosa platform)

Core 2 Duo T7700 - 2.40 GHz (4 MB L2, 800 MHz FSB)

Core 2 Duo T7600 - 2.33 GHz (4 MB L2, 667 MHz FSB)

Core 2 Duo T7500 - 2.20 GHz (4 MB L2, 800 MHz FSB)

Core 2 Duo T7400 - 2.16 GHz (4 MB L2, 667 MHz FSB)

Core 2 Duo T7300 - 2.00 GHz (4 MB L2, 800 MHz FSB)

Core 2 Duo T7250 - 2.00 GHz (2 MB L2, 800 MHz FSB)

Core 2 Duo T7200 - 2.00 GHz (4 MB L2, 667 MHz FSB)

Core 2 Duo T7100 - 1.80 GHz (2 MB L2, 800 MHz FSB)

Core 2 Duo T5600 - 1.83 GHz (2 MB L2, 667 MHz FSB)

Core 2 Duo T5550 - 1.83 GHz (2 MB L2, 667 MHz FSB, no VT)

Core 2 Duo T5500 - 1.66 GHz (2 MB L2, 667 MHz FSB, no VT)

Core 2 Duo T5470 - 1.60 GHz (2 MB L2, 800 MHz FSB, no VT)

Core 2 Duo T5450 - 1.66 GHz (2 MB L2, 667 MHz FSB, no VT)

Core 2 Duo T5300 - 1.73 GHz (2 MB L2, 533 MHz FSB, no VT)

Core 2 Duo T5270 - 1.40 GHz (2 MB L2, 800 MHz FSB, no VT)

Core 2 Duo T5250 - 1.50 GHz (2 MB L2, 667 MHz FSB, no VT)

Core 2 Duo T5200 - 1.60 GHz (2 MB L2, 533 MHz FSB, no VT)

Core 2 Duo L7500 - 1.60 GHz (4 MB L2, 800 MHz FSB) (Low Voltage)

Core 2 Duo L7400 - 1.50 GHz (4 MB L2, 667 MHz FSB) (Low Voltage)

Core 2 Duo L7300 - 1.40 GHz (4 MB L2, 800 MHz FSB) (Low Voltage)

Core 2 Duo L7200 - 1.33 GHz (4 MB L2, 667 MHz FSB) (Low Voltage)

Core 2 Duo U7700 - 1.33 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage)

Core 2 Duo U7600 - 1.20 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage)

Core 2 Duo U7500 - 1.06 GHz (2 MB L2, 533 MHz FSB) (Ultra Low Voltage) - Kentsfield - 65 nm process technology

Two dual-core cpu dies in one package.

Desktop CPU Quad Core (SMP support restricted to 4 CPUs)

Introduced December 13, 2006

same features as Conroe but with 4 CPU Cores

Number of Transistors 586 Million

Socket 775

Family 6, Model 15, Stepping 11

Variants

Core 2 Extreme QX6850 - 3 GHz (2x4 MB L2 Cache, 1333 MHz FSB)

Core 2 Extreme QX6800 - 2.93 GHz (2x4 MB L2 Cache, 1066 MHz FSB) (Apr 9th 07)

Core 2 Extreme QX6700 - 2.66 GHz (2x4 MB L2 Cache, 1066 MHz FSB) (Nov 14th 06)

Core 2 Quad Q6700 - 2.66 GHz (2x4 MB L2 Cache, 1066 MHz FSB) (Jul 22nd 07)

Core 2 Quad Q6600 - 2.40 GHz (2x4 MB L2 Cache, 1066 MHz FSB) (Jan 7th 07) - Wolfdale - 45 nm process technology

Die shrink of Conroe

Same features as Conroe with the addition of:-

50% more cache, 6 MB as opposed to 4 MB

Intel Trusted Execution Technology

SSE4 SIMD instructions

Number of Transistors 410 Million

Variants

Core 2 Duo E8600 - 3.33 GHz (6 MB L2, 1333 MHz FSB)

Core 2 Duo E8500 - 3.16 GHz (6 MB L2, 1333 MHz FSB)

Core 2 Duo E8400 - 3.00 GHz (6 MB L2, 1333 MHz FSB)

Core 2 Duo E8300 - 2.83 GHz (6 MB L2, 1333 MHz FSB)

Core 2 Duo E8200 - 2.66 GHz (6 MB L2, 1333 MHz FSB)

Core 2 Duo E8190 - 2.66 GHz (6 MB L2, 1333 MHz FSB, no TXT, no VT) - Yorkfield - 45 nm process technology

Quad core CPU

Die shrink of Kentsfield

Contains 2x Wolfdale dual core dies in one package

Same features as Wolfdale

Number of Transistors 820 Million

Variants

Core 2 Extreme QX9770 - 3.2 GHz (2x6 MB L2, 1600 MHz FSB)

Core 2 Extreme QX9650 - 3 GHz (2x6 MB L2, 1333 MHz FSB)

Core 2 Quad Q9650 - 3 GHz (2x6 MB L2, 1333 MHz FSB)

Core 2 Quad Q9550 - 2.83 GHz (2x6 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q9550s - 2.83 GHz (2x6 MB L2, 1333 MHz FSB, 65W TDP)

Core 2 Quad Q9450 - 2.66 GHz (2x6 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q9400 - 2.66 GHz (2x3 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q9400s - 2.66 GHz (2x3 MB L2, 1333 MHz FSB, 65W TDP)

Core 2 Quad Q9300 - 2.5 GHz (2x3 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q8300 - 2.5 GHz (2x2 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q8200 - 2.33 GHz (2x2 MB L2, 1333 MHz FSB, 95W TDP)

Core 2 Quad Q8200s - 2.33 GHz (2x2 MB L2, 1333 MHz FSB, 65W TDP)

- Allendale - 65 nm process technology

Desktop CPU (SMP support restricted to 2 CPUs)

Two CPUs on one die

Introduced January 21, 2007

SSSE3 SIMD instructions

Number of Transistors 167 Million

TXT, enhanced security hardware extensions

Execute Disable Bit

EIST (Enhanced Intel SpeedStep Technology)

Variants

Intel Pentium E2220 - 2.40 GHz (1 MB L2, 800 MHz FSB)

Intel Pentium E2200 - 2.20 GHz (1 MB L2, 800 MHz FSB)

Intel Pentium E2180 - 2.00 GHz (1 MB L2, 800 MHz FSB)

Intel Pentium E2160 - 1.80 GHz (1 MB L2, 800 MHz FSB)

Intel Pentium E2140 - 1.60 GHz (1 MB L2, 800 MHz FSB) - Wolfdale 45 nm process technology

Intel Pentium E5400 - 2.70 GHz (2MB L2,800 MHz FSB)

Intel Pentium E5300 - 2.60 GHz (2MB L2,800 MHz FSB)

Intel Pentium E5200 - 2.50 GHz (2MB L2,800 MHz FSB)

- Merom-1024 65 nm process technology

64 KB L1 cache

1 MB L2 cache (integrated)

SSE3 SIMD instructions, 533 MHz front-side bus, execute-disable bit, 64-bit

No SpeedStep technology, is not part of the 'Centrino' package

Variants

520 - 1.60 GHz

530 - 1.73 GHz

540 - 1.86 GHz

550 - 2.00 GHz

- Bloomfield - 45 nm process technology

256 KB L2 cache

8 MB L3 cache

front side bus replaced with QuickPath up to 6.4GT/s

Hyper-Threading is again included. This had previously been removed at the introduction of Core line

781 million transistors

introduced November 17, 2008

Variants

920 - 2.66 GHz

940 - 2.93 GHz

965 (extreme edition) - 3.20 GHz

No comments:

Post a Comment